그래핀 반도체 기판 이용 다양한 소자 기술 기여도 예상

[에너지단열경제]이재철 기자

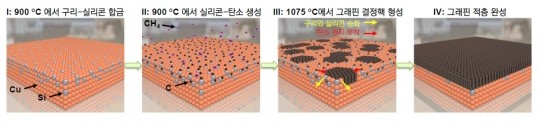

고온에서의 구리-실리콘 합금화 과정부터 균일한 다층 그래핀 성장 과정./IBS 제공

기초과학연구원(IBS) 나노구조물리연구단 이영희 단장과 삼성종합기술원, 부산대 공동 연구진이 4층에 이르는 다층 그래핀을 단결정으로 성장시키는 합성법을 개발했다.

4층짜리 균일한 그래핀은 최초이며, 장비 크기에 따라 수십~수백 제곱센티미터 대면적으로 합성할 수 있어 반도체 고집적 전극 및 다양한 광전극소자등에 응용할 것으로 기대된다.

흑연의 원자 한 층인 그래핀은 우수한 전기전도도와 신축성을 갖춘 데다 투명해서 반도체 전극으로 많이 쓰인다.

또 몇 개의 단층 그래핀이 겹쳐있는지에 따라 응용성이 크게 달라진다. 그래핀을 여러 겹 쌓으면 집적회로의 소형화가 가능하고, 반도체의 특징인 밴드갭을 조절할 수 있다.

그래핀 합성에는 일반적으로 화학기상증착법(CVD)이 쓰인다.

구리와 같은 금속 박막 위에서 그래핀을 성장시키는데, 금속 기판이 촉매 역할을 해 주입된 탄화수소를 분해하고 흡착하는 방법이다.

이때 사용하는 금속의 탄소 용해도에 따라 층수가 조절된다.

구리처럼 낮은 용해도를 가진 금속은 단층 그래핀을 만들고, 니켈처럼 높은 용해도의 금속은 다층 그래핀을 만든다.

그러나 다층 그래핀은 층수가 균일하지 않다는 문제 때문에 고품질의 한계가 있었다.

연구진은 탄소 용해도가 높은 구리 기반 합금을 만드는 데 초점을 맞추고, 구리-실리콘(Cu-Si) 합금을 만드는 방법을 개발했다.

먼저 화학기상증착 장비에서 기판이 들어가는 부분인 석영(SiO₂) 튜브에 구리 기판을 넣고 900도의 고온으로 열처리했다.

튜브에 포함된 실리콘이 기체로 승화돼 구리판에 확산되며 구리-실리콘 합금이 형성된다.

메탄 기체를 주입해, 메탄의 탄소 원자와 석영 튜브의 실리콘 원자가 구리 표면에 균일한 실리콘-탄소(Si-C) 층을 만들도록 했다.

이 층이 앞서 합성한 구리-실리콘 합금의 탄소용해도를 제어한다.

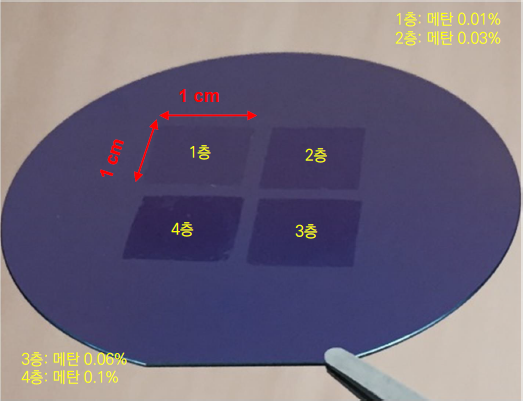

이렇게 만든 기판으로 실험한 결과, 기존의 불균일한 다층 그래핀 합성과는 달리 1, 2, 3, 4층의 균일한 다층 그래핀 제조가 가능해 졌다.

메탄 농도에 따라 층수도 조절됐다.

각 층이 정확히 같은 각도로 겹치면서 반도체 웨이퍼에 견줄 수 있는 크기인데, 대면적 고품질 다층 그래핀을 4층까지 합성한 최초의 연구다.

실리콘 웨이퍼 위에 옮겨진 제곱센티미터 규모의 다층 그래핀. /IBS 제공

이영희 단장은 “이번 연구는 높은 온도의 구리-실리콘 합금 합성을 통해 균일한 다층 그래핀을 성장시킨 새로운 방법으로 기존의 방법으로는 불가능했던 고품질 다층 그래핀 제조에 성공한 것이다”고 밝혔다.

또 “이번 실험을 통해 화학기상증착법으로도 균일한 다층 그래핀 성장이 가능함을 입증했다”고 설명했다.

이번 연구는 구리 전극을 대체할 고집적 전극 및 그래핀을 반도체 기판으로 이용한 다양한 소자 기술에 기여할 것으로 예상된다.

연구진은 앞으로 대량 합성 실험을 반복할 때 석영 튜브가 손상되는 문제를 해결하고 품질 안정성을 높이는 연구를 수행할 예정이다.

이번 연구는 국제학술지 ‘네이처 나노테크놀로지’에 7월 28일 게재됐다.

[ⓒ 케이아이이뉴스-(구)에너지단열경제. 무단전재-재배포 금지]